Semiconductors & VLSI

When Talent Gaps Compromise Yield, Schedules and Silicon Confidence

Semiconductor and VLSI organisations operate in environments where design precision, process discipline and execution timing are unforgiving. A small number of experienced engineers and leaders carry disproportionate responsibility for silicon quality, yield outcomes and delivery timelines.

When critical roles across design, verification, process or manufacturing remain unfilled or underpowered, the impact compounds quickly. Tape-outs slip. Debug cycles extend. Yield risk rises. Leadership loses confidence in schedules and cost assumptions.

Capability Domains That Determine Silicon Success

Semiconductor performance is shaped by a set of tightly coupled capability domains. Each domain represents a distinct form of technical judgment, ownership and execution risk.

Architecture and Front-End Design

This capability defines functional intent, performance targets and power efficiency. Key focus areas include system architecture, RTL design, low-power techniques and design partitioning.

Verification and Validation

Verification capability protects first-pass silicon success. Teams operate across functional verification, coverage closure, constrained-random testing and debug discipline.

Physical Design and Implementation

This domain translates logical designs into manufacturable layouts. It includes floorplanning, timing closure, power integrity, DFT and sign-off readiness.

Process Engineering and Manufacturing Interface

Process capability connects design assumptions with fab realities. Teams manage process integration, yield analysis, defect reduction and fab coordination.

Product Engineering and Post-Silicon Support

Product engineering ensures devices perform reliably in real-world conditions. This includes silicon bring-up, failure analysis, characterisation and customer support.

Why Semiconductor Talent Has Become a Strategic Constraint

The semiconductor industry faces sustained pressure from advanced nodes, heterogeneous integration and global capacity shifts.

What is changing

- Increasing design complexity and node shrink challenges

- Higher cost of errors and respins

- Global competition for experienced VLSI talent

- Compressed timelines driven by market windows

What leaders are experiencing

- Limited availability of engineers with full tape-out exposure

- Rising demand for verification and physical design specialists

- Greater reliance on senior judgment to manage trade-offs

Talent availability now directly shapes yield confidence, schedule integrity and cost control.

How We Support Leadership

- Clarifying design, yield and schedule risk points

- Defining roles around ownership across the silicon lifecycle

- Evaluating candidates through real tape-out and debug scenarios

- Accessing experienced professionals with proven silicon outcomes

Capability Outcomes Leaders Prioritise

- First-pass silicon success

Predictable tape-out and bring-up timelines - Yield stability and cost control

- Strong coordination between design and manufacturing

- Rapid resolution of post-silicon issues

Roles That Anchor Design Integrity and Yield

Certain roles carry disproportionate influence over silicon quality and delivery outcomes.

RTL Design Engineer

Verification Engineer

Frontend Engineer

Experience: 2 to 5 years.

Senior Physical Design Engineer

Senior Product Engineer

Frontend Engineer

Experience: 2 to 5 years.

Director of VLSI Engineering

Head of Semiconductor Operations

Frontend Engineer

Experience: 2 to 5 years.

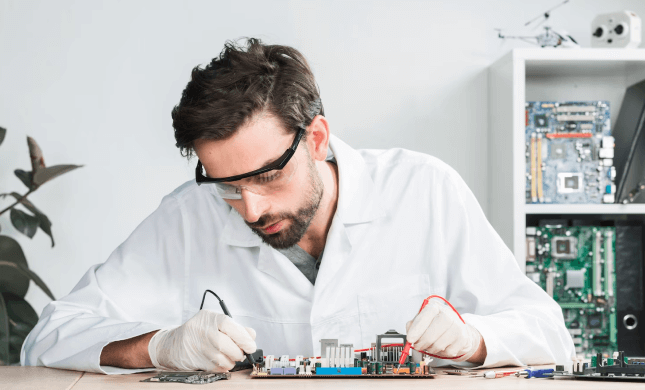

A Hiring Process Built for Silicon Judgment

Semiconductor hiring demands evaluation beyond academic credentials or tool exposure.

Leadership alignment on yield, cost and schedule priorities

Role definitions anchored in lifecycle accountability

Scenario-based discussions drawn from tape-out and failure cases

Assessment of trade-off reasoning and escalation discipline

What Leaders Gain From Capability-Aligned Hiring

When hiring aligns with silicon realities, leaders observe measurable benefits.

Observed Outcomes

- Higher first-pass success rates

- Reduced respins and debug cycles

- Improved yield predictability

- Greater confidence in program timelines

Why Leaders Choose Adept

- Deep understanding of VLSI and semiconductor lifecycles

- Access to seasoned design, verification and product engineers

- Structured evaluation grounded in real silicon scenarios

- Predictable communication and delivery

Trusted by these amazing companies

Testimonials

Adept helped us secure engineers who had real tape-out experience, which reduced execution risk significantly.

Ramesh Iyer

VP Engineering, Fabless Semiconductor Company

The candidates demonstrated strong debug discipline and ownership.

Kavita Nandakumar

Head of Verification, ASIC Design Firm

Our delivery predictability improved once hiring focused on lifecycle accountability.